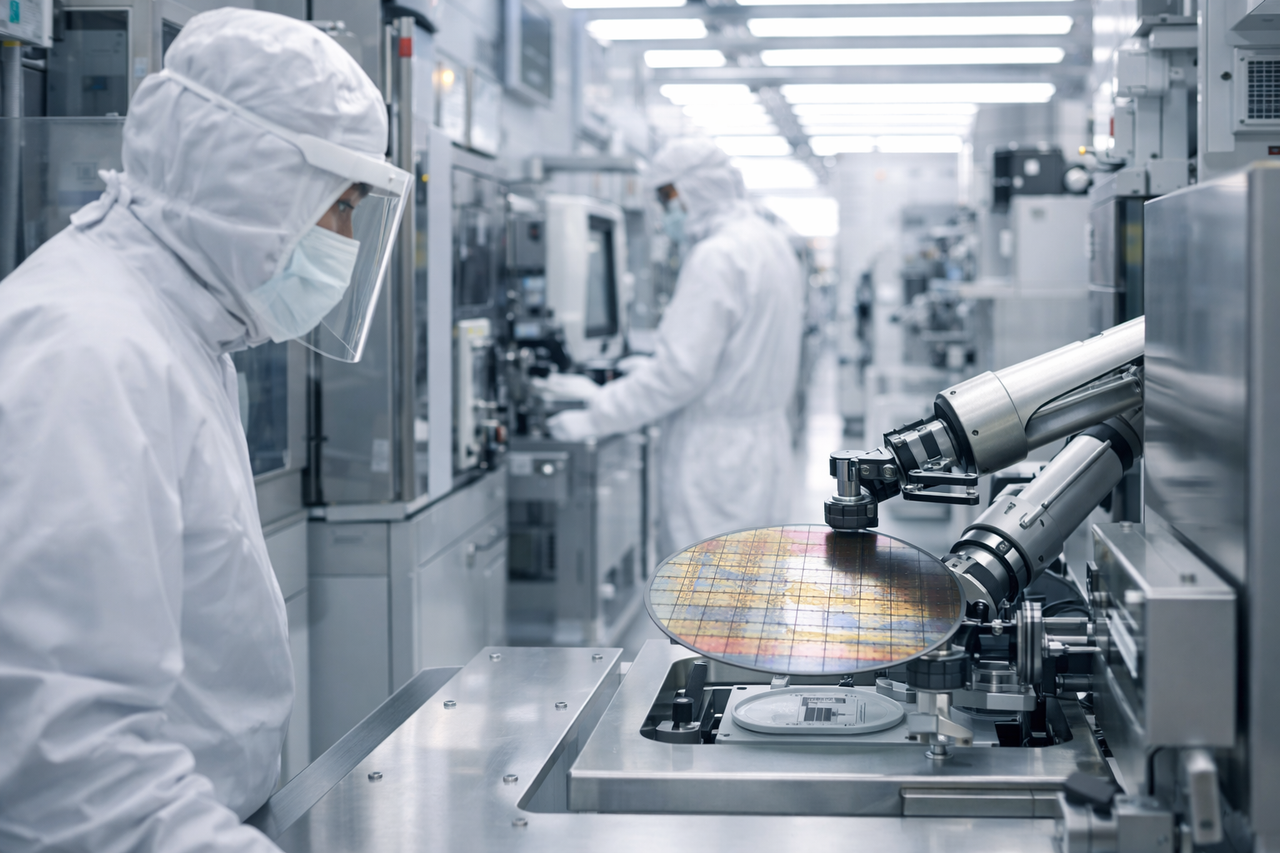

The first thing to understand about India's semiconductor ambitions is the cost of the infrastructure required to realise them. Building a competitive semiconductor fabrication facility is among the most capital-intensive industrial activities in the world, and the costs have been rising as each successive generation of chip technology demands more precise, more complex and more expensive manufacturing equipment. A facility capable of producing chips at the 2nm node, which represents the current frontier of commercial fabrication, costs approximately $28 billion to build, based on TSMC's announced plans for new facilities in Taiwan. A 3nm facility runs to around $20 billion for a plant capable of processing 40,000 wafers per month. Even at the mature 28nm node, which is where India's first approved silicon fabrication project is targeting, construction costs reach approximately $10 billion.

These figures matter because they define the minimum scale of commitment required to enter the industry seriously. India's semiconductor mission offers fiscal support covering up to 50 percent of project costs, per MeitY's published ISM 2.0 terms. That is a meaningful subsidy, and it places India among the more generous jurisdictions in global semiconductor policy. But 50 percent support on a $10 billion mature-node facility still requires $5 billion in private capital from the project sponsor. On a frontier facility, the private exposure would run to $14 billion or more. Attracting that level of private commitment requires not just a subsidy offer but a credible long-term demand environment, a reliable supply chain for process inputs, and confidence in the regulatory and infrastructure framework that will govern the facility's operations for the twenty or thirty years over which the investment needs to generate a return.

There is also the matter of tooling. The machines that make semiconductor chips are themselves among the most complex and expensive objects manufactured anywhere. ASML, the Dutch company that holds a monopoly on extreme ultraviolet lithography systems, sells its standard EUV tool, the Twinscan NXE, for approximately $200 million per unit, based on ASML's own investor relations disclosures. Its next-generation High-NA EUV system, the Twinscan EXE, costs approximately $380 million per machine. A fully equipped advanced-node fab requires dozens of such tools, along with hundreds of other specialised process, metrology and inspection instruments. The capital commitment for equipment alone, before land, buildings or utilities, runs into the billions. India currently has no approved project at a node that would require EUV lithography, but any path toward advanced fabrication capability eventually passes through these cost thresholds.

The global semiconductor industry is one of the most geographically concentrated in the world. According to the Semiconductor Industry Association's 2024 Factbook, United States-headquartered companies hold 50.2 percent of global semiconductor revenue. South Korean firms account for 13.8 percent. European companies hold 12.7 percent, Japanese firms 9 percent, Chinese firms 7.2 percent, and Taiwan-headquartered companies 7 percent. India does not appear in the SIA's market share breakdown, which is itself an accurate reflection of its current position: a significant consumer of semiconductors, a growing participant in chip design, and an absent manufacturer at the fabrication stage.

The Taiwan figure requires a footnote that matters for understanding what India is actually competing against. Taiwan's 7 percent share by company headquarters substantially understates its role in the global industry because it excludes the manufacturing capacity operated on behalf of US and other foreign-headquartered design firms. TSMC alone accounts for more than 60 percent of global contract chip manufacturing by volume. When measured by where chips are physically made rather than where the company that designed them is registered, Taiwan's share of the global semiconductor ecosystem is far larger than the headline revenue figure suggests. India's ambition to become a fabrication hub is therefore not just a competition against other emerging markets. It is an attempt to develop manufacturing capability in a domain that is dominated, at the level of process technology, by a single company in a single island economy that has spent forty years building the knowledge, infrastructure and supplier relationships that make its position almost uniquely difficult to replicate.

India's absence from the fabrication map does not mean it is absent from the semiconductor industry. Between 125,000 and 150,000 semiconductor design engineers are employed in India, according to IESA and MeitY estimates published in 2025 and 2026. India accounts for approximately 20 percent of the global semiconductor design engineering workforce. That is a genuine and significant asset. The design stage of semiconductor development, in which engineers specify the architecture of a chip, define its functional blocks and verify its logical operation before a single wafer is processed, is a high-value, knowledge-intensive activity that can be performed remotely and does not require the physical infrastructure of a fabrication facility.

Almost every major semiconductor company in the world now has a design centre in India. Qualcomm, Intel, AMD, Texas Instruments, Nvidia, ARM and many others employ significant engineering teams in Bengaluru, Hyderabad, Pune and other technology cities. This creates a paradox that is worth being precise about. India's semiconductor engineers are already participating in the creation of some of the world's most advanced chips. They are doing so for companies headquartered in the United States, whose chips are then manufactured in Taiwan or South Korea, assembled in Malaysia or the Philippines, and imported back into India. The intellectual contribution is Indian. The value capture is not.

This is the structural opportunity that India's semiconductor policy is trying to exploit: converting design presence into fabrication presence, and eventually into the kind of integrated design-to-manufacture capability that would allow Indian firms to capture more of the value chain that Indian engineers are already helping to create. The Design Linked Incentive scheme, which offers reimbursement of up to 50 percent of eligible expenditure capped at Rs 15 crore per application and a deployment-linked incentive of 4 to 6 percent capped at Rs 30 crore, is an attempt to encourage domestic design firms to develop India-originated chip designs rather than simply executing design work for foreign principals. Whether the incentive quantum is large enough to shift the behaviour of firms operating in a global design market where the opportunities on offer from US and European companies are considerably larger is a question the scheme's uptake data will eventually answer.

"India accounts for roughly 20 percent of the global semiconductor design engineering workforce. Those engineers are helping design some of the world's most advanced chips, for companies headquartered abroad, whose products are manufactured in Taiwan, and then imported back into India."

India's semiconductor mission is currently embodied in three approved projects at different points along the fabrication and packaging chain. Together they represent a total announced investment of over Rs 1.2 lakh crore, with central fiscal support covering half of eligible project costs. They are the first concrete test of whether India's semiconductor policy framework can attract and sustain the kind of long-horizon industrial commitment that the sector requires.

The Tata Electronics and PSMC joint venture at Dholera in Gujarat is the most strategically significant. It is India's first approved silicon fabrication facility, targeting production at the 28nm node with ambitions to scale to more advanced geometries over time. The investment stands at Rs 91,000 crore, which at current exchange rates represents approximately $10.9 billion, making it one of the largest single industrial investments in India's history. The facility is under construction. A 28nm node is a mature technology by global standards, but mature does not mean easy. The process chemistry, yield management and supply chain requirements of a working silicon fab are formidable for any new entrant, regardless of node. Tata brings genuine industrial scale and the credibility of a domestic champion. PSMC brings Taiwanese process expertise. The combination is plausible. Its success will depend on execution discipline over a multi-year construction and ramp-up period, and on the development of a local supply chain for the hundreds of specialised inputs that a fab consumes.

The Micron ATMP facility at Sanand in Gujarat represents a different but complementary point of entry. Advanced packaging and memory testing does not require the same process precision as front-end fabrication, but it is an important part of the semiconductor supply chain and one where India's improving logistics infrastructure, engineering workforce and labour cost position give it a credible competitive case. Micron's facility, with an investment of Rs 22,516 crore and Phase 1 now operational, is producing real output. It is the clearest current evidence that India can attract and operate a functioning semiconductor facility, and its operational status matters symbolically as well as economically. CG Power's OSAT unit at Sanand, at Rs 7,600 crore and with pilot production underway, adds a domestic industrial champion to a project landscape that had previously been dominated by foreign firms.

| Project | Investment | Type / Node | Location | Status | Strategic Significance |

|---|---|---|---|---|---|

| Tata Electronics and PSMC Joint Venture | ₹91,000 Cr approx. $10.9bn |

Silicon Fab 28nm node |

Dholera, Gujarat | Under Construction | India's first approved silicon fabrication facility. Largest single industrial investment in India's semiconductor history. Tata industrial scale combined with PSMC Taiwanese process expertise. Long-term ambition to advance beyond 28nm. |

| Micron Technology ATMP | ₹22,516 Cr approx. $2.7bn |

Packaging and Testing | Sanand, Gujarat | Phase 1 Operational | First semiconductor facility in India to reach operational status under ISM framework. Validates that India can attract and run a functioning chip-related facility. Produces tangible output and employs semiconductor-grade workers at scale. |

| CG Power (CG Semi) OSAT | ₹7,600 Cr approx. $910m |

Packaging and Testing | Sanand, Gujarat | Pilot Production | First domestic Indian industrial champion to enter semiconductor packaging. CG Power's participation signals that the policy environment is attracting national private capital, not only foreign firms responding to subsidies. |

Semiconductor fabrication makes extraordinary demands on physical infrastructure, and those demands are qualitatively different from those of most other manufacturing sectors. A large fabrication plant consumes between 4.8 and 5 million gallons of water per day, according to research published in ScienceDirect and industry sources in 2025. That is roughly the daily water consumption of a city of 60,000 to 80,000 people, flowing into a single industrial facility. Leading fabs recycle the majority of this volume through on-site treatment systems, but the intake requirement remains enormous and the quality specification for the water is extreme: semiconductor-grade ultra-pure water must meet contamination standards that are among the tightest of any industrial process.

India's water stress position is not a secret. The country is among the most water-stressed large economies in the world, and the regions where its semiconductor facilities are being sited, particularly in Gujarat, face their own groundwater and surface water constraints. The Dholera site has been selected partly because of its planned smart city infrastructure, which includes water management systems. But the long-term question of whether India can sustain, at the scale its semiconductor ambitions require, the water supply infrastructure that fabs demand is one that deserves more prominent treatment in the policy literature than it currently receives.

Power is the parallel constraint, and in some ways the more immediately binding one. Semiconductor fabrication requires uninterrupted, voltage-stable electricity supply. A power fluctuation that would be a minor inconvenience in a textile mill or a food-processing plant can destroy a batch of wafers in a semiconductor fab, writing off hundreds of thousands of dollars of work-in-progress in seconds. India's grid reliability has improved considerably over the past decade, but it has not yet reached the standard that advanced semiconductor manufacturing requires in all locations. The Dholera industrial zone is being developed with dedicated power infrastructure, which is the right approach. The question is whether that infrastructure investment keeps pace with the facility's construction timeline, and whether the supply chain of specialised chemicals, gases and materials that a working fab consumes can be assembled in the same geography before the facility is ready to use them.

Of the three structural constraints facing India's semiconductor ambitions, the one that attracts the least attention in policy documents and the most attention from people who have actually run fabs is tacit manufacturing knowledge. Yield is the term the industry uses for the proportion of chips on a processed wafer that function correctly. In a mature, well-run fab operating a proven process, yields on standard products can exceed 95 percent. In a new fab starting a new process, yields begin much lower and improve gradually as engineers learn, through thousands of iterations, how to control the hundreds of process variables that determine whether a microscopic transistor works or does not. This learning is not transferable through a manual or a training programme. It accumulates in the engineering teams that operate the facility, in the institutional memory of a factory that has been running the same process repeatedly for years, and in the supplier relationships that allow a fab to source consistent-quality inputs reliably.

TSMC did not build its process expertise through a government subsidy scheme. It built it over forty years, through relentless investment in process engineering, through the feedback loops that come from processing millions of wafers for hundreds of customers, and through the institutional culture of a company that treats yield improvement as its primary competitive mission. Samsung's memory manufacturing capability has a similar history. The knowledge that makes these facilities competitive is not patented and cannot be purchased. It is embedded in people and in the operating systems of specific factories.

India's partnership model, which combines domestic capital and industrial management with foreign technology partners such as PSMC, is a pragmatic attempt to shortcut some of this learning curve by importing process expertise alongside the capital investment. This approach is not without precedent: Taiwan itself benefited from technology transfer agreements with RCA and other US firms in the 1970s and 1980s. But technology transfer agreements convey process recipes, not the institutional knowledge that makes those recipes work consistently under real production conditions. The Tata-PSMC venture will learn, and it will improve. The honest question is how long that learning takes, and whether the global semiconductor market will still look the same when Indian fabs have reached competitive yield levels.

A semiconductor fab is not a self-contained facility. It is the anchor of an ecosystem that must surround it, and the competitiveness of the fab depends as much on the quality of that surrounding ecosystem as on the technical capabilities within its own walls. Process chemicals, specialty gases, ultra-pure water treatment systems, photomasks, wafer polishing compounds, abatement systems for hazardous exhaust gases, precision vibration isolation platforms, cleanroom construction specialists, equipment maintenance engineers: each of these inputs is a specialised industry in itself, and in the mature semiconductor ecosystems of Taiwan, South Korea and Japan, each is supplied by firms that are geographically proximate to the fabs they serve, technically capable of meeting the quality specifications those fabs demand, and financially stable enough to invest in the product development that the industry's continuous evolution requires.

India's government has recognised this dependency. The ISM 2.0 policy framework includes allocations targeting specialty gases, semiconductor-grade chemicals, wafer materials and equipment components, alongside the Design Linked Incentive and the flagship fab subsidies. The RISC-V development programme and the expansion of electronic design automation tool access through universities are attempts to broaden the design ecosystem. These are directionally correct interventions. The question, as it is with the broader industrial depth challenge documented in the preceding article in this series, is timing. Building the supplier ecosystem around a new fab requires those suppliers to make their own investment decisions in advance of, or at least in parallel with, the fab they are intended to serve. Suppliers will not invest in building semiconductor-grade chemical production capacity in Gujarat without confidence that there will be a customer for it. That confidence depends on the fab being built, running, and scaling. The chicken-and-egg problem is real, and resolving it requires either state-backed anchor procurement commitments or a sufficiently large cluster of facilities to provide market certainty for the supplier base.

The trajectory from $38 billion in semiconductor imports in FY2023‑24 to a projected $110 billion by 2030 is not simply an economic statistic. It is a description of growing strategic exposure across every sector of the Indian economy that depends on digital infrastructure. Defence systems that rely on specific chip architectures become vulnerable if supply chain disruptions interrupt access to those chips. Telecommunications networks whose base station equipment depends on imported semiconductors are exposed to supply chain leverage from the countries where those chips are made. Electric vehicle manufacturers whose battery management systems, motor controllers and infotainment systems are built around imported chips face cost and availability risks that are entirely outside their control. The import dependency is, in this sense, a sovereignty issue as much as a trade issue, and the government is right to treat it as such.

The realistic near-term contribution of India's fab programme to reducing that import dependency is, however, modest. The Tata-PSMC facility, when operational, will produce chips at the 28nm node. The chips driving the highest-value and most strategically sensitive applications, including advanced AI processors, the most capable smartphone application processors, and the most sophisticated defence electronics, are manufactured at nodes of 7nm or below, which India has no announced plans to produce. India's emerging fab capacity will serve real domestic demand in automotive, industrial and consumer electronics segments where mature-node chips are adequate. It will not, for the foreseeable future, address the most sensitive parts of the import exposure. Acknowledging this distinction is not a counsel of despair. It is a precondition for setting realistic expectations about what the current policy framework can achieve and what the next phase of policy will need to address.

India is not the only country that has identified semiconductor manufacturing as a strategic priority. The United States is investing $52 billion through the CHIPS Act to rebuild domestic fabrication capacity. The European Union has committed to the European Chips Act, targeting a doubling of its global manufacturing share by 2030. Japan is hosting TSMC's first overseas fab at Kumamoto, with a second announced. Saudi Arabia, the UAE and other Gulf states are investing in semiconductor design capabilities as part of their economic diversification programmes. The competitive landscape for attracting semiconductor investment is therefore more crowded and better-funded than it was even three years ago.

India's competitive advantages in this environment are real but specific. Its engineering workforce depth, particularly in chip design, is a genuine differentiator. Its domestic market size provides demand-side rationale for localised production that smaller countries cannot replicate. Its improving logistics infrastructure and its position outside the most acute geopolitical tension zones give it a risk diversification argument that resonates with global firms evaluating China-plus-one strategies. These advantages are sufficient to attract packaging and testing facilities, and potentially to attract mature-node fabrication. They are not yet sufficient, on their own, to attract advanced-node fabrication in competition with the established ecosystems of Taiwan, South Korea, the United States and increasingly Japan.

The window of opportunity created by the current geopolitical disruption to semiconductor supply chains is real. Companies and governments that were comfortable with East Asian concentration in semiconductor manufacturing are now actively seeking alternatives. But that window will not remain open indefinitely. Countries that use it to build genuine manufacturing capability and supplier ecosystems will benefit from first-mover advantages that compound over time. Countries that use it to attract assembly and packaging without developing the deeper ecosystem will find themselves in the same position relative to advanced fabrication as Vietnam is today relative to electronics manufacturing: impressive in volume, constrained in value.

India's semiconductor strategy is more serious and more specifically resourced than anything the country has previously attempted in this sector. The approved projects represent real commitments: a $10.9 billion silicon fab under construction, an operational packaging facility, and a domestic industrial champion entering the market for the first time. The fiscal architecture is credible. The design workforce is a genuine asset. The geopolitical case for India as a diversification destination is real.

What the strategy cannot do, on its own, is compress the timelines that industrial depth requires. Building a competitive fab ecosystem is a fifteen to twenty-year project even under favourable conditions. The knowledge accumulates in people and in processes, not in policy documents or subsidy schedules. The supplier networks develop at the pace of private investment decisions made by hundreds of firms weighing uncertain returns against certain costs. The power and water infrastructure must be built and proven before the facilities that depend on it are operational.

India's semiconductor import bill will continue rising for years regardless of what its fabrication programme achieves in the near term. The honest measure of success for Pax Silica is not whether that bill stops growing in 2030. It is whether, by 2035 or 2040, India has built the ecosystem depth that would make its semiconductor capability durable rather than dependent. That is the assessment that matters, and it is one that no announcement can settle in advance.